PRODUCT

关于我们

-

Product_Information

-

Quality_Assurance

-

INVESTOR_ZONE

Latest News

最新消息

News_title

赋能 AI 与光通信:惠伦晶体高基频工艺产品,定义性能新基准

- 2025.02.Sep

- 325 VIEWS

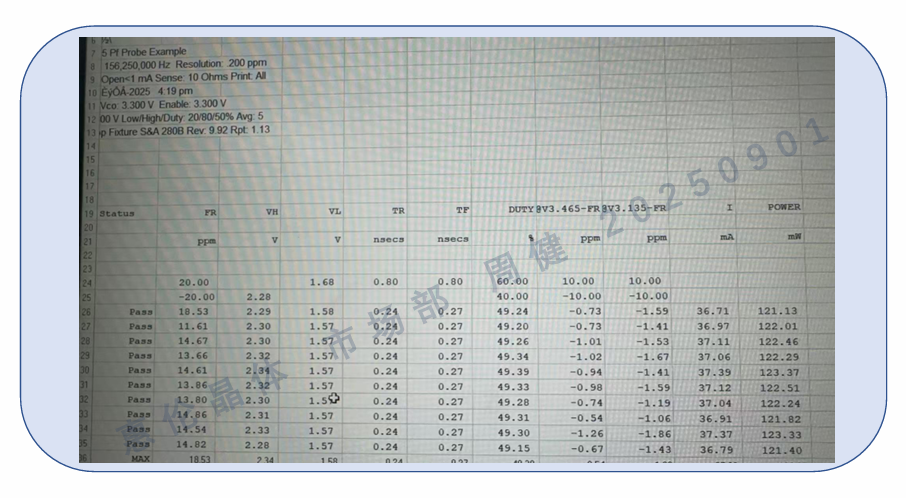

当 AI 服务器向着每秒百亿次运算的算力巅峰冲刺,当光通信模块朝着单通道200Gbps以上的速率突破,作为核心时序源的差分有源晶振,正成为决定系统性能的 “隐形引擎”。惠伦晶体基于尖端基频工艺,推出适配AI服务器与光通信模块的156.25MHz、312.5MHz差分有源晶振,覆盖LVPECL与LVDS两种主流差分接口,以<50fs相位抖动、<0.3nsTr/Tf、±20ppm全场景频率偏差的极致性能,为高端电子设备注入稳定、高速的 “精准心跳”。

一、<50fs 超低相位抖动:破解高速信号的 “干扰密码”

在AI服务器的GPU集群数据交互中,在光通信模块的高速信号调制过程中,相位抖动引发的信号 “微波动”,会直接导致数据同步偏差、误码率上升,成为算力与速率突破的关键瓶颈。惠伦晶体的156.25/312.5MHz差分有源晶振(LVPECL/LVDS),依托基频工艺的深度优化——从晶体谐振腔的精密设计,到振荡电路的噪声抑制,再到封装环节的电磁屏蔽,将相位抖动严格控制在<50fs的超低水平。

对LVPECL接口型号而言,其低噪声输出特性与<50fs抖动结合,可完美适配AI服务器中高速SerDes接口的时序需求,避免因抖动导致的算力损耗;对LVDS接口型号,超低抖动能在光通信模块的信号传输中,减少干扰带来的误码风险,确保 800G/1.6T光模块实现稳定的长距离数据传输,为AI算力释放与光通信高速连接扫清 “干扰障碍”。

同时,传统厂商在进行相位抖动评估时仍然采用频宽12Khz~20Mhz内的中低频抖动,虽能满足一般中高速场景的基础稳定需求,但在更高速率场景中可能存在风险。当场景进入超高速领域(如AI服务器中GPU集群的100Gbps以上数据并行传输、光通信模块中50G/100G速率的信号调制),20Mhz~30Mhz的高频抖动会直接导致 “信号眼图闭合”(眼图是评估信号质量的核心指标),引发误码率上升、数据同步失败等问题。此时,仅评估12Khz~20Mhz区间的抖动已不够——必须确保12Khz~30Mhz全区间的相位抖动<50fs,才能覆盖超高速组件的高频干扰,保障系统在极致速率下的稳定运行。

二、<0.3ns 超快 Tr/Tf:激活系统响应的 “加速引擎”

AI 服务器处理海量并行数据时,芯片间的信号交互需毫秒级响应;光通信模块在高频信号收发中,需快速完成信号的上升与下降转换——这一切都依赖于晶振的Tr/Tf(上升/下降时间)性能。惠伦晶体的差分有源晶振通过基频工艺的电路结构创新,将Tr/Tf压缩至<0.3ns,实现信号状态的 “瞬时切换”。

LVPECL接口凭借更快的边沿速率,可匹配AI服务器中CPU与内存的高速数据交互节奏,减少信号延迟带来的运算效率损失;LVDS接口则以低功耗、低电磁辐射的特性,结合<0.3ns的超快 Tr/Tf,在光通信模块中支撑高频信号的快速调制,助力实现更高带宽的通信传输,让AI算力响应与光信号传输 “快人一步”。

三、±20ppm全场景频率偏差:驾驭复杂环境的 “稳定基石”

AI服务器长期处于高温高负载的机房环境,光通信模块需应对-40℃极寒户外到85℃高温机柜的温度波动,再加上设备运行中的震动、电压波动、负载变化,以及长期使用后的性能老化,都会导致晶振频率偏移,威胁系统稳定性。我们的156.25/312.5MHz 差分有源晶振(LVPECL/LVDS),通过全维度的工艺优化与严苛测试,将全部频率偏差(初始偏差+频率稳定特性偏差+震动影响偏差+电压影响偏差+负载影响偏差+第一年老化偏差)控制在±20ppm,且在-40~85℃宽温范围内持续稳定。

无论是-40℃低温下保障户外光通信模块正常启动,还是85℃高温中支撑AI服务器满负荷运算;无论是应对机房设备震动、电压波动,还是历经一年使用后,LVPECL与 LVDS型号的频率精度始终保持稳定,彻底解决复杂环境下的频率偏移难题,为AI服务器与光通信模块打造 “全天候” 稳定运行的基石。

从AI服务器的算力中枢,到光通信模块的信号核心,惠伦晶体的156.25/312.5MHz基频工艺差分有源晶振(LVPECL/LVDS),以 “超低抖动、超快响应、超稳偏差” 的三重优势,成为高端电子设备的优选时序方案。未来,我们将持续深耕基频工艺与差分接口技术,为 AI 与光通信产业的高速发展提供更精准、更稳定的时序动力!

Quality_Assurance

INVESTOR_ZONE

CONTACT_US

©Copyright 2023 Piezoman All Rights Reserved |

粤ICP备14023153号

中文简体

中文简体

English

English